『图灵完备』完全攻略之存储器(三)

本攻略没有那么追求极致的效率和布局,大佬轻喷。

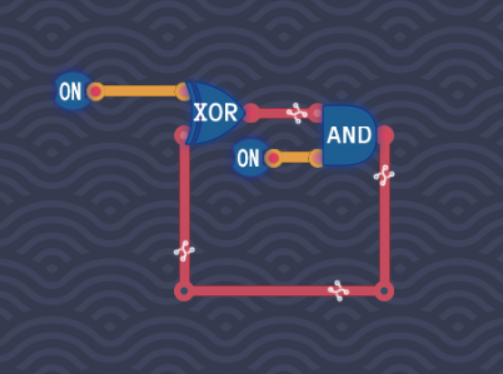

循环依赖

要你搭建一个输出决定输入的错误电路。

延迟线

延迟线元件的体验关卡,根据预期输出可以看到输入延迟了两刻才输出。

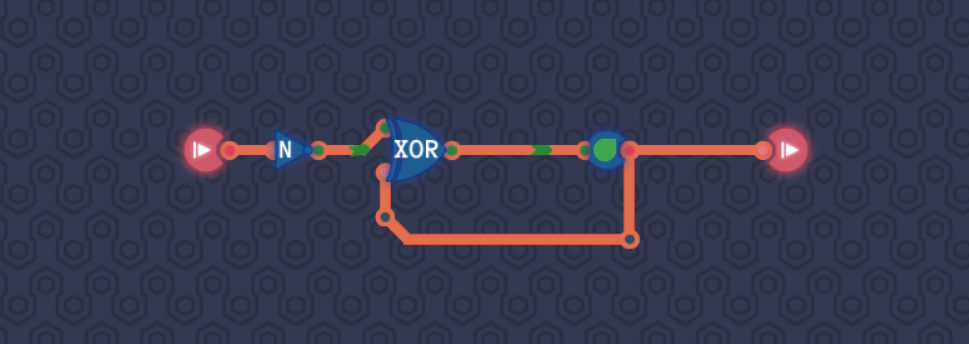

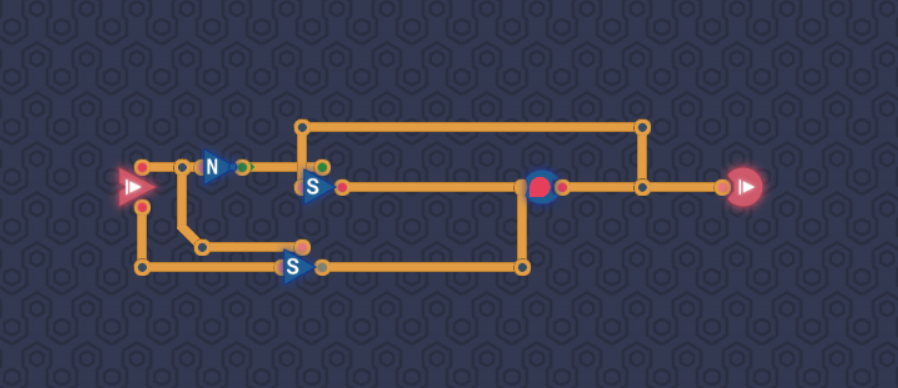

奇变偶不变

关卡告诉我们在延迟的情况下,输出是可以决定输入的。本关卡需要在偶数刻输出高电平,我们利用异或和延迟输出可以做到这一点。

手册解锁了“循环依赖白名单”词条,讲了三种锁存器的实现是不受循环依赖的限制的。

1位取反器

根据反转位决定是否需要对输入进行取反后输出。观察真值表可以发现性质和异或门完全一样。

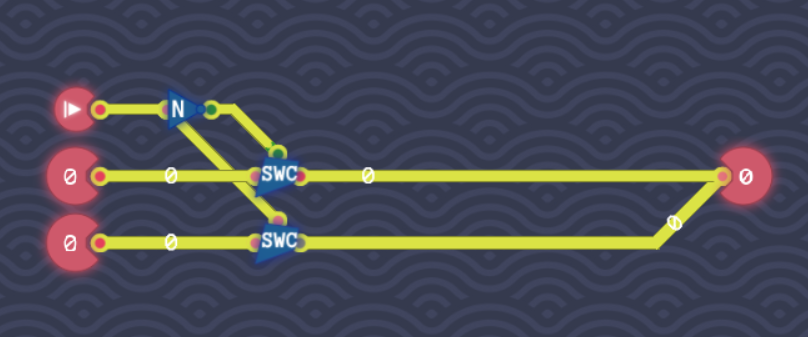

1位开关

用2个开关和2个非门搭建一个异或门。

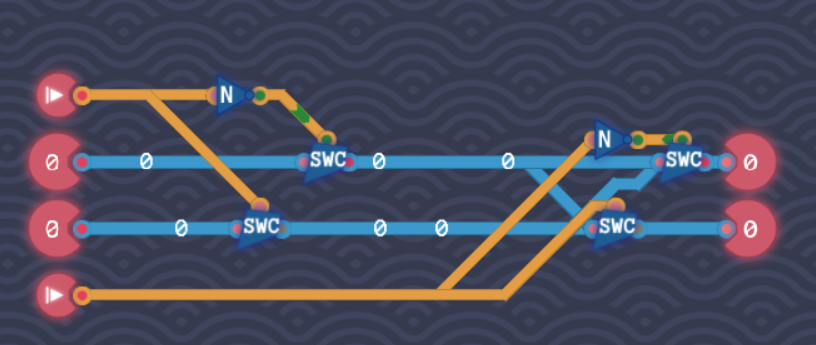

数据选择器

根据选通输入选择一个输入端发送给输出,利用开关和非门就能完成这个电路

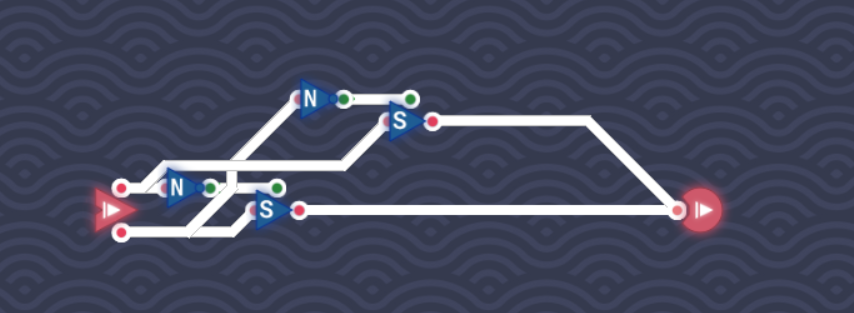

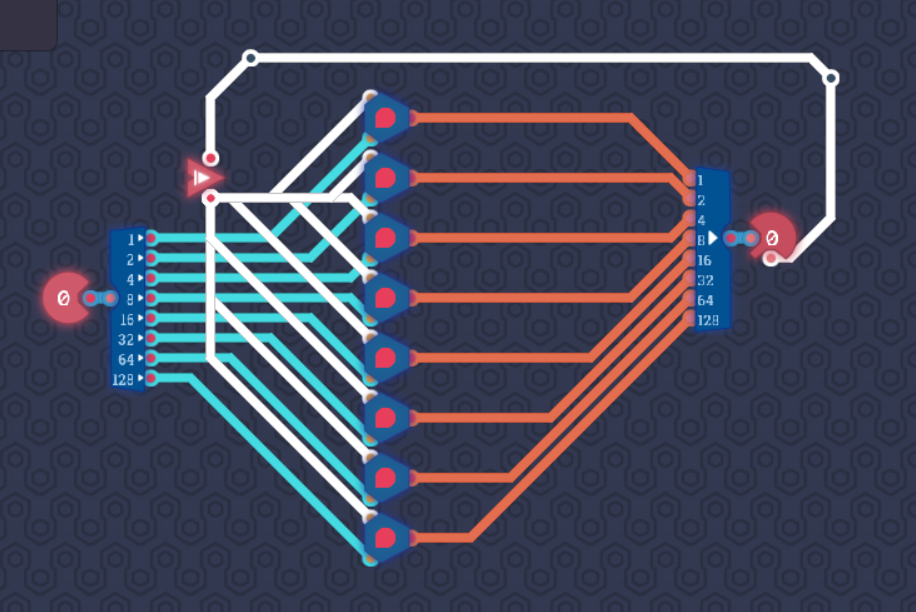

总线

我们可以先布置好每个输入到每个输出的线路,然后再通过布置开关来控制某条线路是否允许通过即可。

但是显然这样子不够优雅,并且也没有体现标题总线。我们知道在一次发送中一定只有一个输入一个输出,因此我们只需要一条线进行数据传输,其他端口都接入这条总线即可。

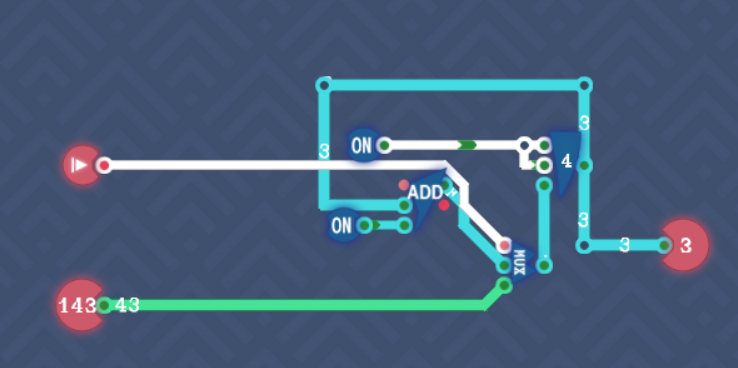

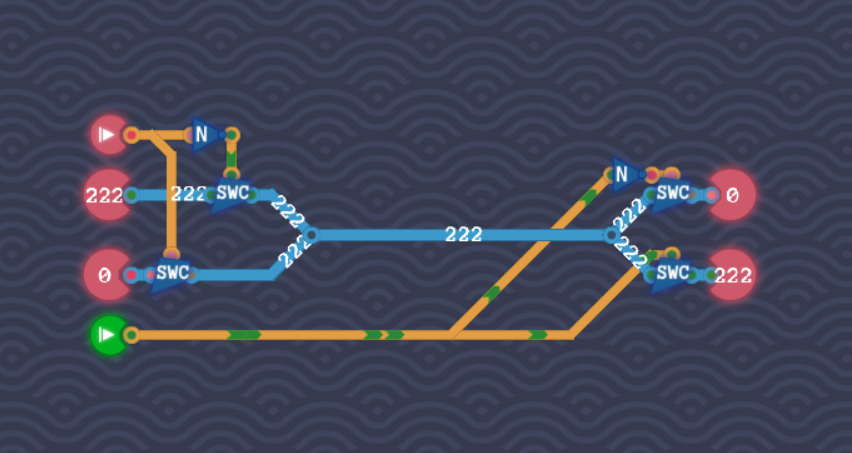

优雅存储

这关其实不难想。延迟线的作用是延迟一刻输出,并且延迟后的输出可以给到输入,那么储存一个数,我们是否可以理解为一直输出这个数,延迟无数刻。那么我只要把延迟后的输出再传入到延迟之前的电路,那我就可以一直输出同一个数字了。那我们要更新数字的时候怎么办呢?只要切断延迟输出回到输入这条路,切换成待写入的值给延迟线即可。

存储一字节

利用1位存储器搭建8位存储器

小盒子

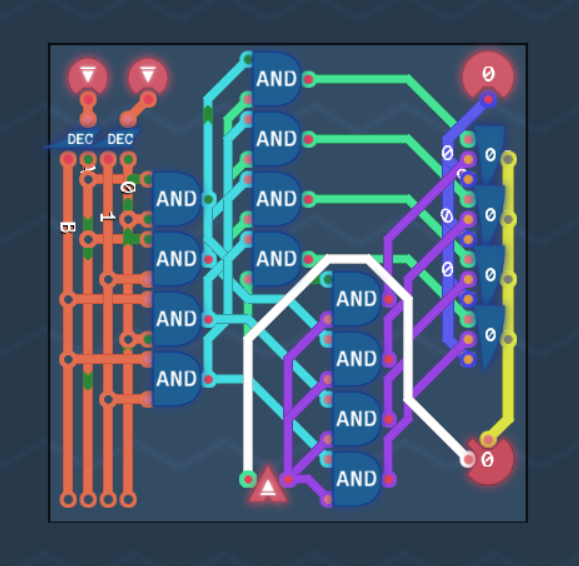

计数器